ARM协处理器CP15(设置MMU,cache等)学习

分享一下我老师大神的人工智能教程!零基础,通俗易懂!http://blog.csdn.net/jiangjunshow

也欢迎大家转载本篇文章。分享知识,造福人民,实现我们中华民族伟大复兴!

作者:wogoyixikexie@gliet

一直对协处理器CP15很恐惧,因为在网上基本上找不到中文的详细说明,现在找了一些ARM官方文档(ARM920T Technical Reference Manual)来看,准备对它做个了结。

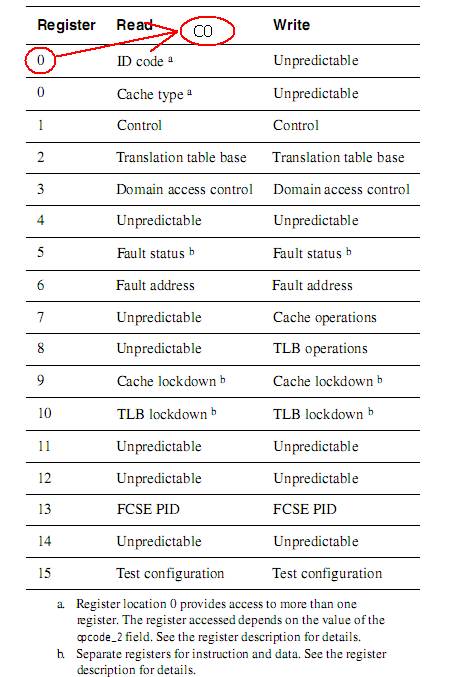

协处理器CP15包含了如下寄存器。

========================================================================

在ARM920T Technical Reference Manual中有如下关键术语

2.3.1 Addresses in ARM920T

Three distinct types of address exist in an ARM920T system:

• Virtual Address (VA)

• Modified Virtual Address (MVA)

• Physical Address (PA).

Below is an example of the address manipulation when the ARM9TDMI core requests

an instruction (see Figure 2-10 on page 2-25).

1. The Instruction VA (IVA) is issued by the ARM9TDMI core.

2. This is translated by the ProcID to the Instruction MVA (IMVA). It is the IMVA

that the Instruction Cache (ICache) and MMU see.

3. If the protection check carried out by the IMMU on the IMVA does not abort, and

the IMVA tag is in the ICache, the instruction data is returned to the ARM9TDMI

core.

4. If the ICache misses (the IMVA tag is not in the ICache), then the IMMU

performs a translation to produce the Instruction PA (IPA). This address is given

to the AMBA bus interface to perform an external access.

_________________________________________________这些东西我就不具体翻译了,免得误人子弟。

2.3.2 Accessing CP15 registers访问CP15 寄存器

The terms and abbreviations(缩写词) shown in Table 2-4 are used throughout this section.

Table 2-4 CP15 abbreviations

Term Abbreviation Description

Unpredictable UNP

For reads, the data returned when reading from this location is unpredictable. It can

have any value.

For writes, writing to this location causes unpredictable behavior, or an unpredictable

change in device configuration.

Should be zero SBZ

When writing to this location, all bits of this field should be 0.

————————————————————————————————————————

You can only access CP15 registers with MRC and MCR instructions in a privileged mode.(特权模式)

MCR/MRC{cond} P15,opcode_1,Rd,CRn,CRm,opcode_2

————

Instructions CDP, LDC, and STC, together with unprivileged MRC and MCR instructions to CP15, cause the undefined instruction trap to be taken(导致未定义...). The CRn field of MRC and MCR instructions specifies the coprocessor register to access. The CRm field and opcode_2 fields specify a particular action when addressing registers. The L bit distinguishes between an MRC (L=1) and an MCR (L=0).——指明了CRn 和CRm 的作用。

————

Note

Attempting to read from a nonreadable register, or to write to a nonwritable register causes unpredictable results.

The opcode_1, opcode_2, and CRm fields should be zero, except when the values specified are used to select the desired operations, in all instructions that access CP15. Using other values results in unpredictable behavior.

——这里用意何在?等到下面看看代码才知道。

————————————————————————————————————————

Register 0, ID code register(读芯片32位ID)

This is a read-only register that returns a 32-bit device ID code.

You can access the ID code register by reading CP15 register 0 with the opcode_2 field set to any value other than 1 (the CRm field should be zero when reading). For example:

MRC p15,0,Rd,c0,c0,0 ; returns ID register

——芯片ID代表含义

Table 2-5 Register 0, ID code

Register bits Function Value

31:24 ——Implementer 0x41——这个是什么意思?

23:20—— Specification revision 0x1

19:16 ——Architecture (ARMv4T) 0x2

15:4—— Part number 0x920

3:0 ——Layout revision Revision

————————————————————————————————————————

2.3.4 Register 0, cache type register

This is a read-only register that contains information about the size and architecture of

the caches, allowing operating systems to establish how to perform such operations as

cache cleaning and lockdown. All ARMv4T and later cached processors contain this

register, allowing RTOS vendors to produce future-proof versions of their operating

systems.

You can access the cache type register by reading CP15 register 0 with the opcode_2 field

set to 1. For example:

MRC p15,0,Rd,c0,c0,1 ; returns cache details

——看上去这个topic特别复杂,我写了也没有用,最重要我极有可能出错,所以停止这篇博客

有什么问题,请到论坛发帖,或者参考

ARM920T Technical Reference Manual——下载地址http://download.csdn.net/source/903240

转载请标明:作者wogoyixikexie@gliet.桂林电子科技大学一系科协,原文地址:http://blog.csdn.net/gooogleman——如有错误,希望能够留言指出;如果你有更加好的方法,也请在博客后面留言,我会感激你的批评和分享。

给我老师的人工智能教程打call!http://blog.csdn.net/jiangjunshow

ARM协处理器CP15(设置MMU,cache等)学习相关推荐

- ARM协处理器CP15介绍

概述 在基于ARM的嵌入式应用系统中,存储系统的操作通常是由协处理器CP15完成的.CP15包含16个32位的寄存器,其编号为0-15.而访问CP15寄存器的指令主要是MCR和MRC这两个指令. MR ...

- (转)ARM协处理器CP15寄存器详解

用于系统存储管理的协处理器CP15 MCR{cond} coproc,opcode1,Rd,CRn,CRm,opcode2 MRC {cond} coproc,opcode1,Rd,CR ...

- ARM协处理器CP15寄存器详解

用于系统存储管理的协处理器CP15 MCR{cond} coproc,opcode1,Rd,CRn,CRm,opcode2 MRC {cond} coproc,opcode1,Rd,CR ...

- ARM协处理器CP15

转自:http://blog.csdn.net/tankai19880619/article/details/8894041 ARM920T = ARM9 core + MMU + Cache MMU ...

- 如何使用ARM协处理器CP15在32位ARRCH模式下操作64位寄存器)

1 参考 参考ARM的官方手册ARMv8指令集架构手册和A53技术参考手册 1.DDI0487H_a_a-profile_architecture_reference_manual 2.DDI0500 ...

- ARM基础学习-协处理器CP15

CP15负责管理ARM中存储管理系统: 常用如下命令来操作CP15的寄存器: MCR{cond} coproc,opc1,CRd,CRn,CRm,opc2 //将arm寄存器中的数据传送到协处理的寄存 ...

- [mmu/cache]-ARM MMU的学习笔记-一篇就够了

★★★ 个人博客导读首页-点击此处 ★★★ . 说明: 在默认情况下,本文讲述的都是ARMV8-aarch64架构,linux kernel 64位 . 相关文章 1.ARM cache的学习笔记-一 ...

- [mmu/cache]-ARM cache的学习笔记-一篇就够了

★★★ 个人博客导读首页-点击此处 ★★★ . 说明: 在默认情况下,本文讲述的都是ARMV8-aarch64架构,linux kernel 64位 . 相关文章 1.ARM MMU的学习笔记-一篇就 ...

- arm 协处理器cp14 cp15

ARM926EJ-S/ARM920T 协处理器 CP14, CP15详解 ARM 微处理器可支持多达 16 个协处理器,用于各种协处理操作,在程序执行的过程中,每个协处理器只执行针对自身的协处理指令, ...

最新文章

- 深度学习时代,调包侠没有未来,但是这个“包”有

- 11步教你选择最稳定的MySQL版本

- 【NLP】万字长文带你解读『虚假新闻检测』最新进展

- 分级显示HTML,SSM框架下,以tree结构分级显示数据

- 玩转GIT系列之【git切换到某个tag之后提示“detached HEAD】

- 独家对话谢宝友:做一款类似于 Linux 的国产操作系统 | 人物志

- JSP语法(JSP动作)

- axis1 c# 接口 调用_java调用c#的Webservice接口数据报错

- 保研论坛app服务器网站,保研论坛官网版app

- 一键去除域名非80端口,去掉域名后面带的端口号快速解决方案

- javascript第二天学习

- 【故障分析】基于matlab ICA故障监测【含Matlab源码 1591期】

- git pull更新不到最新代码

- python早读读后感_《学习Python》读后感摘抄

- Dart factory 快速理解

- 计算机网络传输层课件,计算机网络技术,传输层协议课件

- 微信群发消息怎么发?微信群发消息只需要4步?

- Java面向对象系列[v1.0.0][类加载器]

- Online Judge爬虫

- C语言基础之4:字符串和格式化输入/输出