Camera Link协议和FPGA的数字图像信号源设计

1 引言

目前,各种图像设备已广泛应用到航空航天、军事、医疗等领域。图像信号源作为地面图像采集装置测试系统中的一部分,其传输方式及信号精度都是影响系统性能的重要因素。由于图像信号的传输速率高,数据量大,在传输过程中,其精度和传输距离易受影响。为了提高信号传输距离和精度设计了由FPGA内部发出图像数据,并通过FPGA进行整体时序控制;输出接口信号转换成符合Camera Link标准的低电压差分信号(LVDS)进行传输。该图像信号源已成功应用于某弹载记录器的地面测试台系统中。

2 Camera Link接口及图像数据接口信号

Camera Link标准是由国家半导体实验室(National Semiconductor)提出的一种Channel Link技术标准发展而来的,该接口具有开放式的接口协议,使得不同厂家既能保持产品的差异性,又能互相兼容。它在传统LVDS传输数据的基础上又加载了并转串发送器和串转并接收器,可在并行组合的单向链路、串行链路和点对点链路上,利用SER/DES(串行化/解串行化)技术以高达4.8 Gb/s的速度发送数据。CameraLink标准使用每条链路需两根导线的LVDS传输技术。驱动器接收28个单端数据信号和1个时钟信号,这些信号以7:1的比例被串行发送,也就是5对LVDS信号通道上分别传输4组LVDS数据流和1组LVDS时钟信号,即完成28位数据的同步传输只需5对线,而且在多通道66 MHz像素时钟频率下传输距离可达6 m。

Camera Link是在Channel Link的基础上增加了一些相机控制信号和串行通信信号,定义出标准的接头也就是标准化信号线,让Camera及影像卡的信号传输更简单化,同时提供基本架构(Base Configuration)、中阶架构(Medium Configuration)及完整架构(Full Configuration)三种:基本架构属单一Camera Link元件,为单一接头;中阶架构属双组Camera Link元件,为双组接头;完整架构属三组Camera Link元件,为三组接头。

传输数据时使用的视频同步信号固定不变,分别为: 帧同步信号FVAL:当FVAL为高电平时,正输出一帧有效数据;行同步信号LVAL:当LVAL为高电平时,正输出一个有效像元行(在两个有效像元行中间,LVAL会跳过几个无效的像素点,可在实际应用时设定跳过的像素点数);数据有效信号DVAL:当FVAL和LVAL为高时,DVAL为高电平,正输出有效的数据;SPARE为备用信号。

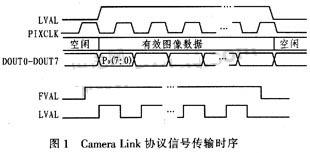

设计中使用了FVAL和LVAL信号,当FVAL和LVAL信号都为高电平时,图像信号源数据在像素时钟信号PIXCLK的控制下依次发送。其接口信号时序如图1所示。

3图像信号源的设计实现

3.1设计方案

检测图像数据记录装置性能、图像信号源的标准图像生成有两种方法。一种是用FPGA直接生成信号,输出图像为0~255的灰度值图像;另一种是通过上位机软件下载图像到信号源中,FPGA产生视频同步信号和进行整体逻辑控制。

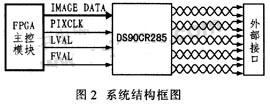

设计中采用了FPGA与Camera Link接口器件DS90CR-285相结合的方案,其图像信号源数据、像素时钟信号及视频同步信号由FPGA内部模块产生,经过DS90CR285器件转换成LVDS信号,接收端使用配套器件DS90CR286进行解调。考虑到FPGA的现场可编程特性,使用灵活方便,能够降低硬件电路设计难度。

所以,该方案选择FPGA作为主模块。Camera Link接口器件DS90CR285是专用电平转换器件,能将28位CMOS/TTL电平数据和一位像素时钟信号分别转换成4组LVDS数据流及一对LVDS时钟信号进行传输,由于采用差分传输方式,提高了传输距离及信号精度。

3.2硬件结构

图2给出图像信号源的硬件结构框图,主要由图像信号源和外围电路组成。前者是设计的核心,它选用Xilinx公司的Spartan-Ⅱ系列FPGAXC2S50,用以设计系统时序、图像数据及产生相应的信号;后者主要包括晶体振荡器、电平转换器件DS90CR285及输入输出接口。

系统上电后,晶体振荡器输出时钟信号,FPGA内部主控模块将自动产生与Camera Link协议相匹配的信号传输时序。FPGA内部产生的像素时钟信号、帧同步信号、行同步信号和图像数据一起进入DS90CR285,并通过该电平转换器件转换成LVDS信号,每对LVDS信号之间采用双绞线传输,以消除耦合干扰。图2中曲线部分即为Camera Link接口。

3.3 FPGA程序设计

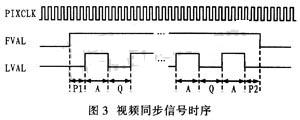

设计中采用VHDL硬件描述语言进行时序设计。系统时钟为125 MHz,信号源像素时钟信号PIXCLK为系统时钟6分频,即21 MHz。本图像信号源数据格式为640×480,帧频为53 Hz,即每秒传输53帧图像。行同步信号LVAL和帧同步信号FVAL均由像索时钟信号进行计数产生,其时序如图3所示。

其中P1为71个PIXCLK时钟周期:A为640个PIXCLK;即一行包含640个像素点;Q为94个PIXCLK;P2为23个PIXCLK,帧同步信号FVAL为低电平的时间是38 074个PIXCLK。一帧图像包含480行有效数据,可计算出传输一帧图像信号的时间为480×(A+Q)+38 074=390 394个PIXCLK时钟周期,帧频为21 MHz÷390 394=53 Hz,满足设计要求。

其中P1为71个PIXCLK时钟周期:A为640个PIXCLK;即一行包含640个像素点;Q为94个PIXCLK;P2为23个PIXCLK,帧同步信号FVAL为低电平的时间是38 074个PIXCLK。一帧图像包含480行有效数据,可计算出传输一帧图像信号的时间为480×(A+Q)+38 074=390 394个PIXCLK时钟周期,帧频为21 MHz÷390 394=53 Hz,满足设计要求。

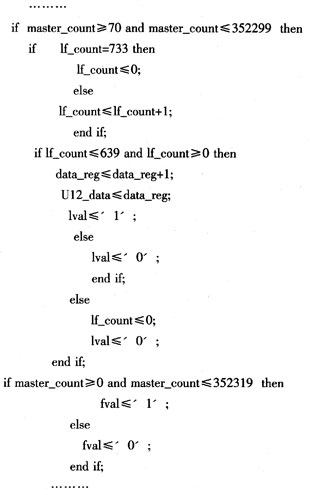

产生行同步信号、帧同步信号和图像数据部分程序代码如下:

上述代码中,lval为行同步信号;fval为帧同步信号;U12_data为图像数据。

3.4实验结果

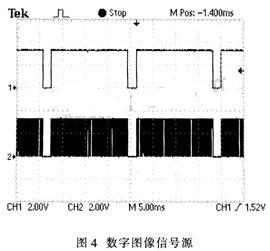

将程序下载到FPGA进行实现。图4给出该图像信号源产生的视频同步信号,即帧同步电压信号Ufval和同步电压信号Ulval。由图4中可见,符合设计时序的要求。

4结语

根据提供的方案,使用FPGA设计的图像信号源结构简单,实现方便,而且具有很强的可扩展性。基于Camera Link接口协议的图像信号采用LVDS方式传输,增加了传输距离,提高了传输过程中的信号精度。在地面测试台系统的应用中,该图像信号源运行稳定、可靠,各项指标均能满足各项设计要求。

Camera Link协议和FPGA的数字图像信号源设计相关推荐

- 基于FPGA的数字视频信号处理器设计(中)

今天给大侠带来基于FPGA的数字视频信号处理器设计,由于篇幅较长,分三篇.今天带来第二篇,中篇,视频信号概述和视频信号处理的框架.话不多说,上货. 之前也有图像处理相关方面的文章,这里超链接几篇,给各 ...

- 基于 FPGA 的数字抢答器设计

下面是基于 FPGA 的数字抢答器设计,在quartusII下,modelsim下仿真,编程语言VHDL. 1.抢答器的工作原理 主持人宣布可以抢答后,在 20s 的定时时间内若有人按键抢答,则这 ...

- 基于FPGA的数字秒表的设计

应用VHDL语言设计数字系统,很多设计工作可以在计算机上完成,从而缩短了系统的开发时间,提高了工作效率.本文介绍一种以FPGA为核心,以VHDL为开发工具的数字秒表,并给出源程序和仿真结果. 1 系统 ...

- 基于FPGA的数字视频信号处理器设计(下)

基于FPGA的数字视频信号处理器设计(下) 今天给大侠带来基于FPGA的数字视频信号处理器设计,由于篇幅较长,分三篇.今天带来第三篇,下篇,程序测试与运行.话不多说,上货. 导读 图像是用各种观测系统 ...

- 基于FPGA的通信信号源设计

verilog实现基于FPGA的通信信号源设计 要求: 能够发射正弦波 对发出的正弦波进行2ask,2fsk,2psk,2dpsk调制 调制时用到PN序列(伪随机序列) 步骤: 第一步:产生两个频率不 ...

- 基于FPGA的数字时钟的设计课设(HUAT)

目录 前言 一.数字时钟课设目标 二.部分代码 1.clock.v代码的编写 2.完整代码 3.仿真代码 总结 前言 学校黄老师的FPGA的设计课设,最后的课设为数字时钟,实现分时的计数功能,带有整点 ...

- m基于FPGA的数字下变频verilog设计

目录 1.算法描述 2.仿真效果预览 3.verilog核心程序 4.完整FPGA 1.算法描述 整个数字下变频的基本结构如下所示 NCO使用CORDIC算法,CIC采用h结构的CIC滤波器,HBF采 ...

- 基于FPGA的数字电子钟的设计与实现-实验报告

系统顶层模块设计 图1 系统顶层设计电路 图2 数字钟功能设计电路 图3 秒表功能设计电路 图4 闹钟功能设计电路 1.1系统功能 该系统分为数字钟.秒表.闹钟三个功能模块,通过开关控制模块key_5 ...

- 基于FPGA的数字电子钟的设计与实现

背景:本实验所有结果基于Quartus II 13.1 (64-bit)实现,实验过程采用自下而上 2020年6月21日更新 我的实验报告,希望大家可以借鉴理解. 链接:https://pan.bai ...

最新文章

- MSMQ 远程计算机不可用 remotemachinenotavailable

- Matlab中*和.*区别

- Spring boot错误处理原理

- 如何将因果干预用于提升模型公平性?

- 电子工程可以报考二建_非工程类专业可以报考二建吗?哪些省份不限制报考专业?...

- Android获取网络状态

- CM:How is the version of word installed in client returned to Application server

- php gzip 关闭,php能否在当前脚本页关闭nginx的gzip输出

- HBase配置(伪分布式模式)

- centos搭建git服务

- android canvas 工作流_行情艰难,Android初中级面试题助你逆风翻盘,每题都有详细答案...

- Linus 谈软件开发管理经验(转载)

- python ssh模块_python ssh之paramiko模块使用

- 创业冲突的五种解决方法是_当创始合伙人发生冲突时,最好的解决方法4和5

- 国际开源固件基金会 (OSFF)组织

- Kali远程控制Android系统(Metasploit)

- exe打包工具,封装exe安装程序--Inno Setup

- 油猴【QQ空间自动点赞-模拟点击】

- 爱老虎油和你探索flash中的对象

- java邮件撤回_JavaMail 退回邮件

热门文章

- oracle注册表误删怎么恢复,误删注册表后如何恢复,regedit.exe文件不存在!!!

- linuxmint20.1 wine QQ不显示图片问题解决办法

- 2014秋C++ 狗逮耗子之“开口说英语”

- 打包软件——Setup factory 7.0使用介绍

- php只能小程序访问,百度智能小程序支付 - 冯奎博客 — 再牛逼的梦想,也抵不住你傻逼似的坚持。 — Fengkui Blog...

- 都能看懂的LIS(最长上升子序列)问题

- SV学习笔记—function函数和task任务

- Redis未授权访问漏洞复现(三种方式)

- ExtJs学习(一)~~ 简述概念

- VMware Workstation Pro虚拟工具