HPS基本概念及其设计

DE1-SOC开发版上的FPGA在一个基于ARM的用户定制系统(SOC)中集成了分立处理器(HPS)、FPGA和数字信号处理(DSP)功能。HPS是基于ARM cortex-A9双核处理器,具有丰富的外设和存储接口(DDR2/3)等。 HPS 和 FPGA 不仅能够独立工作,也能通过高性 能 AXI 总线桥接实现高速宽带行数据通信,这个总线是双向的,HPS 总线主机能够通过 HPS 至 FPGA 桥接访问 FPGA 架构中的总线及其外设。所有桥接兼容 AXI-3/4, 支持同时读写操作,同样的,FPGA 架构中的总线主机能够通过 FPGA 至 HPS 桥接访问 HPS 总线及其外设。基本架构如下:

1、本文学习目的

- 建立一个 SoC based FPGA hardware 系统

- HPS 组件在 Qsys 内的设定(based on DE1-SoC board)

- FPGA avmm 外设和 HPS 桥接

- 生成 Preloader 和 Device Tree(based on DE1-SoC board)

- 编译 linux 应用程序 Linux 下控制 HPS 的外设

- HPS 总线到 FPGA 总线的 Address Mapping

- HPS 控制 FPGA 端的 LED(based on DE1-SoC board)

2、基本设计流程

SoC FPGA 设计流程 基于 SoC 的 FPGA 嵌入式系统硬件与软件的开发流程如图所示。

首先要基于 Qsys 规划系统需要的外设,包括 HPS 与 FPGA 各自的接口。HPS 外设只需要根据 DE1-SoC 硬 件属性进行设定即可,FPGA 外设依旧是通过 IP 模块的方式添加。然后建立各个模块间 的连接(时钟,复位,总线),最后产生出硬件与软件开发各自所需的档案

- 硬件开发和以往传统的基于 NiosII 的 FPGA 设计流程相同,使用 Quartus 加入 Qsys 以 及用户逻辑,然后设定 FPGA 管脚分配,最后综合编译产生 .sof 编程档案。

- 软件的开发则通过 Altera 的 SoCEDS 开发工具将 Qsys 所做的 HPS 硬件设定转换成产生 Preloader、uboot 和 Device Tree 所需的输入文件。这些文件可以协助 HPS 在 DE1-SoC 上运行 embedded linux system,linux 内核解析需要挂载硬件外设并完成 boot。然后 开发基于 linux 操作系统的应用程序并在 DE1-SoC 上运行。应用程序可以实现 HPS 和 FPGA 协同工作完成定制化设计。

3、boot sd card制作流程

一般从系统设计开始到生成boot linux操作系统SD Card,其所需要的软件工具与生成档案如下:

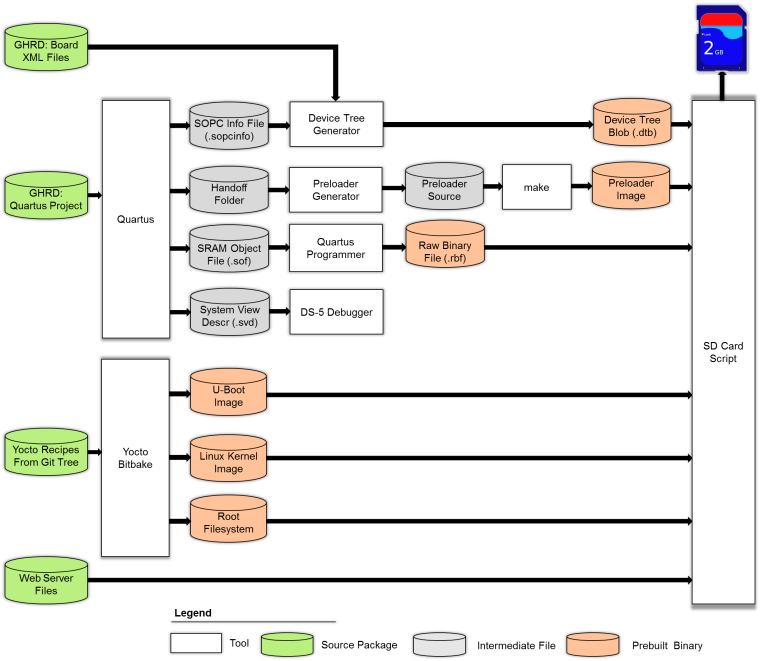

下图说明了GSRD的完整构建流程。

下表显示了构建流程中使用的工具:

| 工具 | 描述 | 部分 |

|---|---|---|

| Quartus II | 创建,编辑和编译FPGA硬件设计 | ACDS |

| 设备树生成器 | 生成设备树 | SoC EDS |

| 设备树编译器 | 在设备树文件格式之间转换 | |

| 预加载器生成器 | 根据硬件切换信息生成Preloader源代码 | |

| ARM DS-5 AE | 软件开发套件 | |

| BitBake的 | Yocto建立实用程序 | Yocto源包 |

| SD卡脚本 | 创建SD卡图像的脚本 |

下表显示了构建过程中的输入文件:

| 文件 | 描述 |

|---|---|

| Quartus项目 | FPGA硬件项目源代码 |

| Board XML文件 | 描述开发板的文件,用于创建设备树 |

| Yocto食谱 | 用于构建Linux可交付成果的Yocto配方 |

| Web服务器文件 | 在板上运行的Web服务器所需的其他文件 |

下表描述了构建流程图中的其余项目:

| 文件 | 描述 |

|---|---|

| .sof | SRAM目标文件 - FPGA编程文件,由编译FPGA硬件项目产生 |

| .rbf | 原始二进制文件 - 压缩FPGA编程文件 |

| .dts | 设备树源 - 用于描述Linux内核的硬件 |

| .dtb | 设备树二进制 - .dts的二进制表示 |

| .sopcinfo | SOPC信息文件 - 包含设备树生成器要使用的硬件的描述 |

| .svd | 系统视图描述文件 - 描述DS-5调试器的硬件 |

| 不可触摸 | 包含Preloader Generator要使用的硬件描述的文件夹 |

4、搭建Qsys系统

下面开启Qsys工程,了解HPS的组件设定。

1、创建Qsys工程

Qsys工程的创建过程不是这里的重点,了解创建过程可以参考文章完整的SOPC开发流程体验,这里直接打开官方培训给的工程(提取码dhgv,不要放到中文路径下)

进入de1_soc_training\de1_soc_training\lab\HW\DE1_SoC_GHRD,双击soc_system.qpf打开工程

点击Qsys打开Qsys工具 ,打开.qsys系统,可以看到里面已经包含了HPS等组件

,打开.qsys系统,可以看到里面已经包含了HPS等组件

2、配置HPS系统

HPS内包含了双核的ARM Cortex A9处理器外,还由许多内建外设可以使用。

下面对其进行配置,点击hpc_0打开HPS配置窗口 ,可以看到如下配置界面,HPS属性有FPGA Interfaces、PeripheralPin Multiplexing、HPS Clock和SDRAM四个配置栏。

,可以看到如下配置界面,HPS属性有FPGA Interfaces、PeripheralPin Multiplexing、HPS Clock和SDRAM四个配置栏。

在FPGA Interfaces选项栏下,在general下的选项是配置使能基本的接口和信号,配置AXI Bridges参数

AXI Bridges可以配置3个AXI Bridges的数据宽度

FPGA to HPS SDRAM Interface下可以增减FPGA to HPS SDRAM的接口数目

Resets可以配置系统的Reset信号

DMA Peripheral Request使能以及中断使能

HPS-to-FPGA使能外围设备。

在Peripheral Pin Multiplexing选项栏下,可以通过选项来启动HPS的外围设备。

可以看到每一个外设都有一个pin选项,这是因为HPS I/O如果对照DE1-SOC的原理图,可以发现HPS的管脚是复用的,这个就需要对照着原理图进行配置。可以参照友晶DE-SOC开发板的user manual

在这个设定页最底下也提供了Peripherals Mux Table,可以帮助用户检验整个HPS外设I/O pin multiplexing设定的状态,看看是否有冲突。表内,若管脚名被标注为粗体,就代表此管脚一杯设定。

在HPS Clocks选项卡,可以设置使能 HPS to FPGA和FPGA to HPS之间的时钟及其频率.17.0软件中Cyclone V 器件MPU 默认时钟为925Mhz,而13.1版为800M。这里编译不改变MPU的Clock,所以去掉use default MPU clock frequency选项!不用改其他的选项,Clock即为800MHz。重新generate 关闭就好了。使用Quarut编译编译完成后会有hps_isw_handoff中的文件会更新,这些文件时连接HPS硬件配置与preloaderr软 件接口文件。

在SDRAM选项卡里,你可以配置HPS的外部存储器接口参数。

这里只做简单介绍采用默认配置,实际工程中根据需求进行配置。

3、添加并配置组件

接下来,就是根据需求在Qsys里加入组件并与HPS连接。这里用LED进行举例。

1、组件添加与配置

首先添加LED PIO component,在IP catalog中搜索PIO,选中PIO,双击添加组件

添加过程需要对组件进行配置,因为是10个LED,所以配置如下:

点击finish后,在Qsys里就可以看到添加的组件。此时还有报错,这是应为没进行连接。

2、组件重命名

为了便于区分不同IO的作用,此处需要对组件重命名,选中PIO->右键->选择rename(或者选中CTRL+R)

然后,双击extern_connection的Export栏,引出LED的外部线,将其重命名为led_pio_external_connection

同理添加四个input按键

3、组件连线

将组件按如下方式连线

可以通过如下方法连接,,右键led_pio组件下的clk信号,选择要来连接的信号,依次相连即可。

其中需要注意的是在button_pio中,因为是输入,会有中断优先极设置,其连线如下

设置优先等级,选择IRQ列,分配IRQ优先级,这里设为1

4、基地址设置

将led_pio的基地址修改为0x01_0040,将button_pio 的基地址基地址修改为0x01_00C0地址分配参照下图。

关于地址还有一个需要理解的(来自WS_2_Linux_Kernel_Introduction_Workshop):

并点击锁定图标锁定基地址,如图所示

至此,整个组件已经添加完毕,完整系统连接如图所示。

点击generate hdl进行编译保存即可。

4、搭建Qsys系统

当 Qsys 生成完后,会产生出许多可以被 Quartus II 编译合成的 HDL(verilog) 文档,一般位于以qsys文件名命名的文件夹内。这些文件需要先被增添入Quartus II 工程内。我们可以通过增加 .qip 这个描述所有文件位置的目录档案完成所有 include 文档的包含。

如图所示在 Quartus II 下选择 Assignments => Settings

然后在(<你的路径>\de1_soc_training\de1_soc_training\lab\HW\DE1_SoC_GHRD\soc_system\synthesis)添加.qip文件

使用同样的方法,将文件夹(<你的路径>\de1_soc_training\de1_soc_training\lab\HW\DE1_SoC_GHRD)下的时序约束文件soc_system_timing.sdc加入到项目中

点击apply后,回到quartus ii界面,在project Navigator中,双击ghrd_top

可以开ghrd_top.v文件,找到soc_system u0,在期内加入led_pio和button_pio对应的instance输入LED以及Button的外部接口声明信号。

.led_pio_external_connection_export (LEDR),

.button_pio_external_connection_export (KEY),

加入后的程序如下:

// Copyright (c) 2013 by Terasic Technologies Inc.

// ============================================================================

//

// Permission:

//

// Terasic grants permission to use and modify this code for use

// in synthesis for all Terasic Development Boards and Altera Development

// Kits made by Terasic. Other use of this code, including the selling

// ,duplication, or modification of any portion is strictly prohibited.

//

// Disclaimer:

//

// This VHDL/Verilog or C/C++ source code is intended as a design reference

// which illustrates how these types of functions can be implemented.

// It is the user's responsibility to verify their design for

// consistency and functionality through the use of formal

// verification methods. Terasic provides no warranty regarding the use

// or functionality of this code.

//

// ============================================================================

//

// Terasic Technologies Inc

// 9F., No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan

//

//

// web: http://www.terasic.com/

// email: support@terasic.com

//

// ============================================================================

//Date: Mon Jun 17 20:35:29 2013

// ============================================================================`define ENABLE_HPS

//`define ENABLE_USBmodule ghrd_top(/ ADC /output ADC_CS_n,output ADC_DIN,input ADC_DOUT,output ADC_SCLK,/ AUD /input AUD_ADCDAT,inout AUD_ADCLRCK,inout AUD_BCLK,output AUD_DACDAT,inout AUD_DACLRCK,output AUD_XCK,/ CLOCK2 /input CLOCK2_50,/ CLOCK3 /input CLOCK3_50,/ CLOCK4 /input CLOCK4_50,/ CLOCK /input CLOCK_50,/ DRAM /output [12:0] DRAM_ADDR,output [1:0] DRAM_BA,output DRAM_CAS_n,output DRAM_CKE,output DRAM_CLK,output DRAM_CS_N,inout [15:0] DRAM_DQ,output DRAM_LDQM,output DRAM_RAS_N,output DRAM_UDQM,output DRAM_WE_N,/ FAN /output FAN_CTRL,/ FPGA /output FPGA_I2C_SCLK,inout FPGA_I2C_SDAT,/ GPIO /inout [35:0] GPIO_A,inout [35:0] GPIO_B,/ HEX0 /output [6:0] HEX0,/ HEX1 /output [6:0] HEX1,/ HEX2 /output [6:0] HEX2,/ HEX3 /output [6:0] HEX3,/ HEX4 /output [6:0] HEX4,/ HEX5 /output [6:0] HEX5,`ifdef ENABLE_HPS/ HPS /

// input HPS_CLOCK1_25,

// input HPS_CLOCK2_25,inout HPS_CONV_USB_N,output [14:0] HPS_DDR3_ADDR,output [2:0] HPS_DDR3_BA,output HPS_DDR3_CAS_N,output HPS_DDR3_CKE,output HPS_DDR3_CK_N,output HPS_DDR3_CK_P,output HPS_DDR3_CS_N,output [3:0] HPS_DDR3_DM,inout [31:0] HPS_DDR3_DQ,inout [3:0] HPS_DDR3_DQS_N,inout [3:0] HPS_DDR3_DQS_P,output HPS_DDR3_ODT,output HPS_DDR3_RAS_N,output HPS_DDR3_RESET_N,input HPS_DDR3_RZQ,output HPS_DDR3_WE_N,output HPS_ENET_GTX_CLK,inout HPS_ENET_INT_N,output HPS_ENET_MDC,inout HPS_ENET_MDIO,input HPS_ENET_RX_CLK,input [3:0] HPS_ENET_RX_DATA,input HPS_ENET_RX_DV,output [3:0] HPS_ENET_TX_DATA,output HPS_ENET_TX_EN,inout [3:0] HPS_FLASH_DATA,output HPS_FLASH_DCLK,output HPS_FLASH_NCSO,inout [1:0] HPS_GPIO,inout HPS_GSENSOR_INT,inout HPS_I2C1_SCLK,inout HPS_I2C1_SDAT,inout HPS_I2C2_SCLK,inout HPS_I2C2_SDAT,inout HPS_I2C_CONTROL,inout HPS_KEY,inout HPS_LED,

// input HPS_RESET_N,output HPS_SD_CLK,inout HPS_SD_CMD,inout [3:0] HPS_SD_DATA,output HPS_SPIM_CLK,input HPS_SPIM_MISO,output HPS_SPIM_MOSI,inout HPS_SPIM_SS,input HPS_UART_RX,output HPS_UART_TX,input HPS_USB_CLKOUT,inout [7:0] HPS_USB_DATA,input HPS_USB_DIR,input HPS_USB_NXT,output HPS_USB_STP,

// output HPS_WARM_RST_N,

`endif /*ENABLE_HPS*// IRDA /input IRDA_RXD,output IRDA_TXD,/ KEY /input [3:0] KEY,/ LEDR /output [9:0] LEDR,/ PS2 /inout PS2_CLK,inout PS2_CLK2,inout PS2_DAT,inout PS2_DAT2,/ SW /input [9:0] SW,/ TD /inout TD_CLK27,output [7:0] TD_DATA,output TD_HS,output TD_RESET_N,output TD_VS,`ifdef ENABLE_USB/ USB /input USB_B2_CLK,inout [7:0] USB_B2_DATA,output USB_EMPTY,output USB_FULL,input USB_OE_N,input USB_RD_N,input USB_RESET_N,inout USB_SCL,inout USB_SDA,input USB_WR_N,

`endif /*ENABLE_USB*// VGA /output VGA_BLANK_N,output [7:0] VGA_B,output VGA_CLK,output [7:0] VGA_G,output VGA_HS,output [7:0] VGA_R,output VGA_SYNC_N,output VGA_VS

);//=======================================================

// REG/WIRE declarations

//=======================================================

wire hps_fpga_reset_n;//=======================================================

// Structural coding

//=======================================================

soc_system u0 ( .clk_clk (CLOCK_50), // clk.clk.reset_reset_n (1'b1), // reset.reset_n.led_pio_external_connection_export (LEDR),.button_pio_external_connection_export (KEY),//HPS ddr3.memory_mem_a ( HPS_DDR3_ADDR), // memory.mem_a.memory_mem_ba ( HPS_DDR3_BA), // .mem_ba.memory_mem_ck ( HPS_DDR3_CK_P), // .mem_ck.memory_mem_ck_n ( HPS_DDR3_CK_N), // .mem_ck_n.memory_mem_cke ( HPS_DDR3_CKE), // .mem_cke.memory_mem_cs_n ( HPS_DDR3_CS_N), // .mem_cs_n.memory_mem_ras_n ( HPS_DDR3_RAS_N), // .mem_ras_n.memory_mem_cas_n ( HPS_DDR3_CAS_N), // .mem_cas_n.memory_mem_we_n ( HPS_DDR3_WE_N), // .mem_we_n.memory_mem_reset_n ( HPS_DDR3_RESET_N), // .mem_reset_n.memory_mem_dq ( HPS_DDR3_DQ), // .mem_dq.memory_mem_dqs ( HPS_DDR3_DQS_P), // .mem_dqs.memory_mem_dqs_n ( HPS_DDR3_DQS_N), // .mem_dqs_n.memory_mem_odt ( HPS_DDR3_ODT), // .mem_odt.memory_mem_dm ( HPS_DDR3_DM), // .mem_dm.memory_oct_rzqin ( HPS_DDR3_RZQ), // .oct_rzqin//HPS ethernet .hps_0_hps_io_hps_io_emac1_inst_TX_CLK ( HPS_ENET_GTX_CLK), // hps_0_hps_io.hps_io_emac1_inst_TX_CLK.hps_0_hps_io_hps_io_emac1_inst_TXD0 ( HPS_ENET_TX_DATA[0] ), // .hps_io_emac1_inst_TXD0.hps_0_hps_io_hps_io_emac1_inst_TXD1 ( HPS_ENET_TX_DATA[1] ), // .hps_io_emac1_inst_TXD1.hps_0_hps_io_hps_io_emac1_inst_TXD2 ( HPS_ENET_TX_DATA[2] ), // .hps_io_emac1_inst_TXD2.hps_0_hps_io_hps_io_emac1_inst_TXD3 ( HPS_ENET_TX_DATA[3] ), // .hps_io_emac1_inst_TXD3.hps_0_hps_io_hps_io_emac1_inst_RXD0 ( HPS_ENET_RX_DATA[0] ), // .hps_io_emac1_inst_RXD0.hps_0_hps_io_hps_io_emac1_inst_MDIO ( HPS_ENET_MDIO ), // .hps_io_emac1_inst_MDIO.hps_0_hps_io_hps_io_emac1_inst_MDC ( HPS_ENET_MDC ), // .hps_io_emac1_inst_MDC.hps_0_hps_io_hps_io_emac1_inst_RX_CTL ( HPS_ENET_RX_DV), // .hps_io_emac1_inst_RX_CTL.hps_0_hps_io_hps_io_emac1_inst_TX_CTL ( HPS_ENET_TX_EN), // .hps_io_emac1_inst_TX_CTL.hps_0_hps_io_hps_io_emac1_inst_RX_CLK ( HPS_ENET_RX_CLK), // .hps_io_emac1_inst_RX_CLK.hps_0_hps_io_hps_io_emac1_inst_RXD1 ( HPS_ENET_RX_DATA[1] ), // .hps_io_emac1_inst_RXD1.hps_0_hps_io_hps_io_emac1_inst_RXD2 ( HPS_ENET_RX_DATA[2] ), // .hps_io_emac1_inst_RXD2.hps_0_hps_io_hps_io_emac1_inst_RXD3 ( HPS_ENET_RX_DATA[3] ), // .hps_io_emac1_inst_RXD3//HPS QSPI .hps_0_hps_io_hps_io_qspi_inst_IO0 ( HPS_FLASH_DATA[0] ), // .hps_io_qspi_inst_IO0.hps_0_hps_io_hps_io_qspi_inst_IO1 ( HPS_FLASH_DATA[1] ), // .hps_io_qspi_inst_IO1.hps_0_hps_io_hps_io_qspi_inst_IO2 ( HPS_FLASH_DATA[2] ), // .hps_io_qspi_inst_IO2.hps_0_hps_io_hps_io_qspi_inst_IO3 ( HPS_FLASH_DATA[3] ), // .hps_io_qspi_inst_IO3.hps_0_hps_io_hps_io_qspi_inst_SS0 ( HPS_FLASH_NCSO ), // .hps_io_qspi_inst_SS0.hps_0_hps_io_hps_io_qspi_inst_CLK ( HPS_FLASH_DCLK ), // .hps_io_qspi_inst_CLK//HPS SD card .hps_0_hps_io_hps_io_sdio_inst_CMD ( HPS_SD_CMD ), // .hps_io_sdio_inst_CMD.hps_0_hps_io_hps_io_sdio_inst_D0 ( HPS_SD_DATA[0] ), // .hps_io_sdio_inst_D0.hps_0_hps_io_hps_io_sdio_inst_D1 ( HPS_SD_DATA[1] ), // .hps_io_sdio_inst_D1.hps_0_hps_io_hps_io_sdio_inst_CLK ( HPS_SD_CLK ), // .hps_io_sdio_inst_CLK.hps_0_hps_io_hps_io_sdio_inst_D2 ( HPS_SD_DATA[2] ), // .hps_io_sdio_inst_D2.hps_0_hps_io_hps_io_sdio_inst_D3 ( HPS_SD_DATA[3] ), // .hps_io_sdio_inst_D3//HPS USB .hps_0_hps_io_hps_io_usb1_inst_D0 ( HPS_USB_DATA[0] ), // .hps_io_usb1_inst_D0.hps_0_hps_io_hps_io_usb1_inst_D1 ( HPS_USB_DATA[1] ), // .hps_io_usb1_inst_D1.hps_0_hps_io_hps_io_usb1_inst_D2 ( HPS_USB_DATA[2] ), // .hps_io_usb1_inst_D2.hps_0_hps_io_hps_io_usb1_inst_D3 ( HPS_USB_DATA[3] ), // .hps_io_usb1_inst_D3.hps_0_hps_io_hps_io_usb1_inst_D4 ( HPS_USB_DATA[4] ), // .hps_io_usb1_inst_D4.hps_0_hps_io_hps_io_usb1_inst_D5 ( HPS_USB_DATA[5] ), // .hps_io_usb1_inst_D5.hps_0_hps_io_hps_io_usb1_inst_D6 ( HPS_USB_DATA[6] ), // .hps_io_usb1_inst_D6.hps_0_hps_io_hps_io_usb1_inst_D7 ( HPS_USB_DATA[7] ), // .hps_io_usb1_inst_D7.hps_0_hps_io_hps_io_usb1_inst_CLK ( HPS_USB_CLKOUT ), // .hps_io_usb1_inst_CLK.hps_0_hps_io_hps_io_usb1_inst_STP ( HPS_USB_STP ), // .hps_io_usb1_inst_STP.hps_0_hps_io_hps_io_usb1_inst_DIR ( HPS_USB_DIR ), // .hps_io_usb1_inst_DIR.hps_0_hps_io_hps_io_usb1_inst_NXT ( HPS_USB_NXT ), // .hps_io_usb1_inst_NXT//HPS SPI .hps_0_hps_io_hps_io_spim1_inst_CLK ( HPS_SPIM_CLK ), // .hps_io_spim1_inst_CLK.hps_0_hps_io_hps_io_spim1_inst_MOSI ( HPS_SPIM_MOSI ), // .hps_io_spim1_inst_MOSI.hps_0_hps_io_hps_io_spim1_inst_MISO ( HPS_SPIM_MISO ), // .hps_io_spim1_inst_MISO.hps_0_hps_io_hps_io_spim1_inst_SS0 ( HPS_SPIM_SS ), // .hps_io_spim1_inst_SS0//HPS UART .hps_0_hps_io_hps_io_uart0_inst_RX ( HPS_UART_RX ), // .hps_io_uart0_inst_RX.hps_0_hps_io_hps_io_uart0_inst_TX ( HPS_UART_TX ), // .hps_io_uart0_inst_TX//HPS I2C1.hps_0_hps_io_hps_io_i2c0_inst_SDA ( HPS_I2C1_SDAT ), // .hps_io_i2c0_inst_SDA.hps_0_hps_io_hps_io_i2c0_inst_SCL ( HPS_I2C1_SCLK ), // .hps_io_i2c0_inst_SCL//HPS I2C2.hps_0_hps_io_hps_io_i2c1_inst_SDA ( HPS_I2C2_SDAT ), // .hps_io_i2c1_inst_SDA.hps_0_hps_io_hps_io_i2c1_inst_SCL ( HPS_I2C2_SCLK ), // .hps_io_i2c1_inst_SCL//HPS GPIO .hps_0_hps_io_hps_io_gpio_inst_GPIO09 ( HPS_CONV_USB_N), // .hps_io_gpio_inst_GPIO09.hps_0_hps_io_hps_io_gpio_inst_GPIO35 ( HPS_ENET_INT_N), // .hps_io_gpio_inst_GPIO35.hps_0_hps_io_hps_io_gpio_inst_GPIO40 ( HPS_GPIO[0]), // .hps_io_gpio_inst_GPIO40.hps_0_hps_io_hps_io_gpio_inst_GPIO41 ( HPS_GPIO[1]), // .hps_io_gpio_inst_GPIO41.hps_0_hps_io_hps_io_gpio_inst_GPIO48 ( HPS_I2C_CONTROL), // .hps_io_gpio_inst_GPIO48.hps_0_hps_io_hps_io_gpio_inst_GPIO53 ( HPS_LED), // .hps_io_gpio_inst_GPIO53.hps_0_hps_io_hps_io_gpio_inst_GPIO54 ( HPS_KEY), // .hps_io_gpio_inst_GPIO54.hps_0_hps_io_hps_io_gpio_inst_GPIO61 ( HPS_GSENSOR_INT), // .hps_io_gpio_inst_GPIO61//FPGA soft GPIO .dipsw_pio_external_connection_export ( SW ), // dipsw_pio_external_connection.export//HPS reset output .hps_0_h2f_reset_reset_n (hps_fpga_reset_n), // hps_0_h2f_reset.reset_n);endmodule打开tools->tcl script,选择hps_sdram_p0_assignments.tcl进行引脚分配

可以看到引脚已经分配成功

点击编译生成.sof文件,接着连接FPGA上电点击 将生成的文件烧写进去即可。

将生成的文件烧写进去即可。

5、验证FPGA部分组件

因为此系统是Qsys生成的,含有jtag to avammbridge,所以可以用Qsys的System Console完成初步的验证工作。System Console通过jtag和qsys avmm及连接的components进行数据通信,这一般通过使用tcl脚本命令完成。

打开Qsys并打开之前生成的.qsys文件,选择Tools->System Console,打开系统控制台,如下图所示

选择File-> Execute Script,弹出如下窗口,这里选择不创建

定位到<你的路径>/DE1_SOC/GHRD,选择test_led.tcl打开

可以看到脚本文件已经成功执行。

开发板上,可以看到LEDR0~9依次循环点亮。

同样的方法执行test_key&led.tcl脚本

用手保持按下 KEY0 按钮,然后选择“打开”test_key&led.tcl 文件,在 message 窗口下你会看到提示信息:0x0e 0x00,同时在 DE1-SOC 开发板上,你将 看到 LEDR0 未点亮,其他三个 LEDR 是亮的。然后松掉 KEY0,LEDR0 也不会亮。(即 保持按下 KEY0~3 中的其中几个按钮,然后执行脚本文件,你会发现 message 打印 出按键向量值,DE1-SoC 开发板上,按键未按下时值是 1,按下为 0,LEDR 是高电 平点亮,这里直接把按键值赋值给 LED,所以按下的按键对应的 LED 是熄灭的)程序逻辑在altera_edge_detector.v文件中

实验现象如下:

参考资料

altera官方培训文档及资料

转载于:https://www.cnblogs.com/noticeable/p/9378394.html

HPS基本概念及其设计相关推荐

- TF学习——Tensorflow框架之基础概念、设计思路、常用方法之详细攻略

TF学习--tensorflow框架之基础概念.设计思路.常用方法之详细攻略 目录 Tensorflow框架基础概念 Tensorflow框架设计思路 Tensorflow框架常用方法 Tensorf ...

- 分布式系统概念和设计 第十五章 (1)

COORDINATION AND AGREEMENT http://www.cdk5.net/wp/ 背景知识点:Reliable failure detector 实际系统中没有reliable f ...

- 分布式系统概念和设计-操作系统中的支持和设计

分布式系统概念和设计 操作系统支持 中间件和底层操作系统的关系,操作系统如何满足中间件需求. 中间件需求:访问物理资源的效率和健壮性,多种资源管理策略的灵活性. 任何一个操作系统的目标都是提供一个在物 ...

- 红点奖设计概念奖设计之星奖

1.引言 有角动物智能放牧机器人的最后设计稿获得了设计概念奖设计之星奖,今年该最高奖项的获奖率不到0.8%. 这一方面体现了我公司在动物穿戴设计领域的领先,也体现了我们对动物自身感受的感知获得了国际上 ...

- 《数据库系统》(四) 概念数据库设计

hello大家好,今天我们来学习概念数据库设计.教妹学数据库,没见过这么酷炫的标题吧?"语不惊人死不休",没错,标题就是这么酷炫. 我的妹妹小埋18岁,校园中女神一般的存在,成绩优 ...

- 分布式系统概念和设计——特征,实例,Web,Future

分布式系统概念和设计 分布式系统的特征 关于分布式系统的定义产生的结论 并发性,如何协调并发执行的共享资源型的程序 缺乏全局时钟,程序协作需要通过交换信息完成,紧密的协调依赖于对程序动作发生时的时间共 ...

- 计算机算法的概念教案,“算法的概念”教学设计.pdf

2017年第 1-2期 中国数学教育 №1- 2.2017 (总第169- 70期) ZHONGGUO SHUXUEJA|oYU Genera1.No16争一170 "算法的概念''教学设计 ...

- 分布式系统概念和设计——分布式多媒体系统

分布式系统概念和设计 分布式多媒体系统 QoS QoS(Quality of Service,服务质量)是一种网络管理和控制技术,可以对网络流量进行管理和调度,以确保网络对不同类型的数据流的传输可以提 ...

- 数字滤波器概念及设计

数字滤波器概念及设计 数字滤波器分类 滤波器相关函数 常见滤波器 平均滤波器 平滑滤波器 限幅滤波器 中值滤波器 数字滤波器(digital filter)是一个离散时间系统,通常按照预定的算法,将输 ...

最新文章

- 来客推开源商城与你浅析:B2B2C多商户商城系统

- TortoiseSVN使用详细步骤(一)

- 注册时发短信如何防止别人恶意调用短信接口

- 神经网络有可能被公式化表达吗?

- Java中的基本数据类型以及Java的基本结构

- 去掉“3_人民日报语料”中每行前边的数字编号,改成“1, 2,......”

- angularjs全栈开发知乎_为什么你要去尝试全栈开发?

- appium 搭建及实例

- 决定c++语言中函数的返回值类型的是,全国2009年10月高等教育自学考试C++程序设计试题及部分参考答案...

- viewController详解

- 正则表达式收集(持久更新)

- 基于JAVA+SpringMVC+Mybatis+MYSQL的学生考勤管理系统

- 流程控制库async

- 区分大小屏幕_新GL8陆尊30多万,四块屏幕,科技感堪比奔驰,你还选埃尔法吗?...

- ibm刀片服务器如何装系统,详细分析如何安装和配置IBM刀片服务器

- 风险模型—VaR模型2

- 嵌入式开发 | 嵌入式开发设计文档该怎么写?

- 网易云音乐部门技术面

- Vue中 使用vue-particles(粒子背景)插件美化登录页面

- 高新企业申报是什么?需要怎么申请?