Spartan-6的时钟资源、全局时钟缓冲器/多路复用器

时钟资源

时钟布线资源具有高速、低SKEW的特点,它对系统设计非常重要,即使系统速率不高,也应该关注时钟设计,以消除潜在的时钟危险。Spartan-6器件包含16个全局时钟资源和40个I/O区域时钟资源。全局时钟用于系统时钟,而I/O区域时钟专用于I/O串行/解串(ISERDES和OSERDES)设计。

Spartan-6时钟资源包含以下4种。

全局时钟输入引脚(GCLK)。局时钟多路复用器。I/O时钟缓冲器。时钟布线网络。

包括由BUFGMUX驱动的全局时钟网络和由I/O时钟缓冲器(BUFIO2)、PLL时钟缓冲器(BUFPLL)驱动的I/O区域时钟网络。

一、 时钟输入

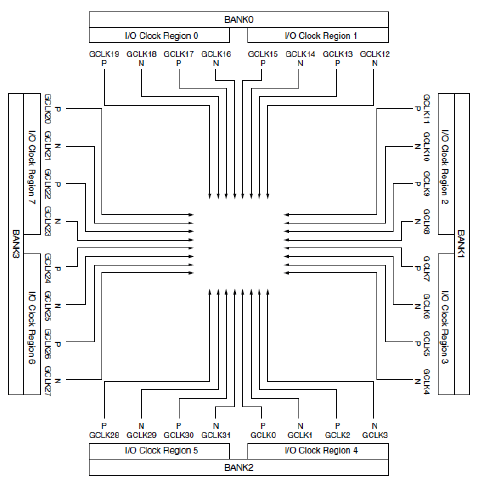

每个Spartan-6有32个全局时钟输入引脚,分布在FPGA的四周。时钟输入引脚在片上的分布图如图2-5所示。时钟输入引脚接收外部时钟信号,直接连接片内的DCM/PLL/BUFGMUX/BUFIO2。时钟输入引脚不连接时钟时,用作普通I/O。

一个差分时钟输入需要两个全局时钟输入。成对的时钟输入在标号上是连续的,例如,GCLK0和GCLK1是差分对,GCLK20和GCLK21是差分对。每个全局时钟缓冲器有两个时钟输入,Spartan-6支持最多16对的差分全局时钟输入。

设计中的时钟输入引脚连接IBUFG原语,通常综合工具会分析设计,自动将顶层时钟引脚推演为与IBUFG相连。如果需要更多IBUFG的控制功能,可以通过例化IBUFG的方式,将IBUFG的I端口连到顶层端口,将O端口连接到DCM、BUFG或通用逻辑。

图2-5 时钟输入引脚片上分布图

图2-5 时钟输入引脚片上分布图

HDL代码中例化全局输入缓冲器(IBUFG)的原语参见表2-6。

表2-6 全局输入缓冲器(IBUFG)的原语

表2-6 全局输入缓冲器(IBUFG)的原语

原文地址:点击打开链接

全局时钟缓冲器/多路复用器

Spartan-6的时钟缓冲器/多路复用器(BUFG或BUFPLL)可以直接驱动时钟输入信号到时钟线上,或者通过多路复用器在两个不相关的信号甚至异步时钟信号中切换。

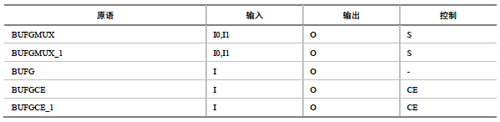

全局时钟缓冲器的原语如表2-7所示。

表2-7 全局时钟缓冲器/多路复用器的原语

表2-7 全局时钟缓冲器/多路复用器的原语

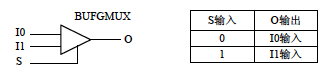

(1) BUFGMUX。

BUFGMUX可以作为一个BUFG,或者作为两个全局时钟源的多路选择器在两个时钟源之间切换。BUFGMUX只驱动全局时钟布线资源。通用布线资源也能驱动FPGA逻辑触发器上的时钟输入,但是通常不推荐使用,因为通用布线资源有较高的SKEW。

如图2-6所示,BUFGMUX是具有两个时钟输入I1 和I0、一个时钟输出O和一条选择线S的时钟缓冲器,可以消除两个时钟源之间切换时产生毛刺信号。选择线S必须满足建立时间要求,违反这一建立时间可能导致毛刺信号。

图2-6 BUFGMUX原语

图2-6 BUFGMUX原语

选择线S翻转选择另一个时钟源输出时,输出保持在一个非活动态直到下一个有效时钟沿到来。当两个时钟切换时,输出电平可以为高电平或低电平,缺省为低电平。交叉解耦寄存器确保了BUFGMUX 输出不会产生一个时钟脉冲边沿。

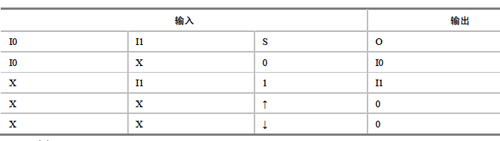

当S输入改变时,输出保持为Low,直到另一(待选)时钟从High 转为Low。然后,新的时钟开始驱动输出,如表2-8 所示,由于输入第一个低到高的跳变输出不翻转,所以,输出不会比最短输入时钟脉冲短。

S输入为低,选择时钟输入I0;S输入为高,选择时钟输入I1。BUFGMUX还具有内置可编程极性,等效于交换I0和I1。每个触发器可以对时钟信号进行极性设置,确定上升沿或下降沿触发,避免产生两个不同的时钟信号。

表2-8 BUFGMUX功能表

表2-8 BUFGMUX功能表

(2) BUFGMUX_1。

BUFGMUX_1和BUFGMUX功能相同,区别在于BUFGMUX_1对上升沿敏感,并且在输入切换之前保持为High。

(3) BUFG。

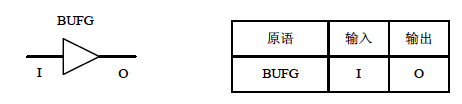

如图2-7所示,BUFG其实就是具有一个时钟输入和一个时钟输出的时钟缓冲器,它也是Virtex 和Spartan器件中时钟缓冲器的通用原语。

图2-7 BUFG的原语

图2-7 BUFG的原语

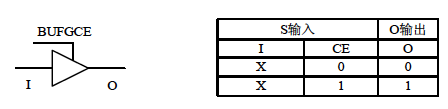

(4) BUFGCE 和BUFGCE_1。

BUFGCE是具有一个时钟输入、一个时钟输出和一条时钟使能线的时钟缓冲器。当时钟使能CE为高,输入I 经缓冲器输出;当CE为低(非激活状态),输出O为低。其原语如图2-8所示。

图2-8 BUFGCE的原语

图2-8 BUFGCE的原语

BUFGCE_1与BUFGCE功能相同,不同的是,当时钟使能CE为低时,输入I 经缓冲器输出;当CE为高(非激活状态),输出O为高。

Spartan-6的时钟资源、全局时钟缓冲器/多路复用器相关推荐

- UltraScale时钟资源和时钟管理模块

UltraScale时钟资源和时钟管理模块 绪论 图2.1和2.2给出了UltraScale结构的时钟结构.从图中可以看出,基本的结构是由表示分段时钟行和列的CR块构成的CR以一个单元的方式排列,从而 ...

- Virtex-6器件的时钟资源、混合模式时钟管理器(MMCM)

时钟资源 为了更好的控制时钟,Virtex-6器件分成若干个时钟区域,最小器件有6个区域,最大器件有18个区域.每个时钟区域高40个CLB.在时钟设计中,推荐使用片上专用的时钟资源,不推荐使用本地时钟 ...

- 赛灵思FPGA中的主要时钟资源介绍

把握DCM.PLL.PMCD 和MMCM 知识是稳健可靠的时钟设计策略的基础. 赛灵思在其FPGA 中提供了丰富的时钟资源,大多数设计人员在他们的FPGA 设计中或多或少都会用到.不过对FPGA设计新 ...

- XILINX FPGA时钟资源

Xilinx FPGA时钟资源 Xilinx FPGA时钟包括全局时钟资源.局部时钟资源和I/O时钟资源.Xilinx FPGA除了提供丰富的时钟网络之外,还提供了强大的时钟管理模块,并不断改进,从V ...

- Xilinx FPGA内部资源之时钟篇1

以下时钟介绍以Virtex5系列芯片作为参考芯片 从时钟的角度可以将Xilinx FPGA划分为若干个时钟域(Clock Region),不同的FPGA芯片具有不同数量的时钟域,XC5VLX30有8个 ...

- cpld xilinx 定义全局时钟_AutoSAR中的时钟同步机制

Fig 1 AutoSar CP中的时间同步部分主要由Stbm,TimeSyncOverEth和底层的以太网模块组成. 底层的以太网模块主要负责收发报文和时间戳. 如果系统设计决定使用网卡NIC的时钟 ...

- Xilinx FPGA全局时钟和第二全局时钟资源的使用方法

目前,大型设计一般推荐使用同步时序电路.同步时序电路基于时钟触发沿设计,对时钟的周期.占空比.延时和抖动提出了更高的要求.为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时 ...

- (30)FPGA面试题全局时钟资源及原语

1.1 FPGA面试题全局时钟资源及原语 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA面试题全局时钟资源及原语: 5)结束语. 1.1.2 本节引言 &quo ...

- bufg和bufgp_Xilinx FPGA全局时钟和第二全局时钟资源的使用方法(转)

"全局时钟和第二全局时钟资源"是FPGA同步设计的一个重要概念.合理利 用该资源可以改善设计的综合和实现效果:如果使用不当,不但会影响设计 的工作频率和稳定性等,甚至会导致设计的综 ...

最新文章

- 策略梯度搜索:不使用搜索树的在线规划和专家迭代 | 技术头条

- golang 切片 接口_Go 经典入门系列 18:接口(一)

- Github远程推送一直Everything up-to-date

- C# Windows服务相关

- 结合eShopOnWeb全面认识领域模型架构

- Android listview item中使用TextWatcher

- cad转dxf格式文件太大_想知道DWG、DWT、DWS和DXF是什么吗?从了解4种CAD图形格式开始吧...

- Redis高级特性介绍及实例分析

- h3c s5500-28c-si操作

- 面试题——C++/C

- vue中dom元素和组件的获取

- 华为紧急调试鸿蒙;首个 5G 全覆盖国家诞生;Flutter 1.7 正式发布 | 极客头条

- 如何做好数据安全治理

- 易语言mysql编程助手_编程助手app下载-编程助手安卓版 v7.0.1 - 安下载

- 模拟登录人人网,豆瓣

- 在ie6下实现position-fixed的效果

- excel 的lookup和sumifs函数使用

- 总有人问我:独立站该怎么玩?3个案例,你看完就懂了

- emui华为java2p_同属华为,却是两个相对独立的系统,Magic系统和EMUI区别在哪?...

- 使用OpenDaylight界面下发流表

热门文章

- android跳转到支付宝扫码,【笔记】通过adb shell启动支付宝扫码登录

- 推荐系统算法_机器学习和推荐系统(二)推荐算法简介

- 为什么在反向传播中感知器初始值不能为0_人工智能可以为我们做什么?世界皆可二分类...

- 公司内部多表查询 sql在实现类的应用

- PHP编译为静态库,Linux下将Tinyxml编译为静态库

- matlab fminimax 多变量,Matlab应用实例(8)—fminimax

- java 文件写入 读取_JAVA文件的两种读取方法和三种写入方法

- Apriltag可用图片:TAG16H5

- 第十六届智能车竞赛比赛进行中 - 参赛队员提出的问题

- 2021年春季学期-信号与系统-第十五次作业参考答案